1.后仿真提参选项问题

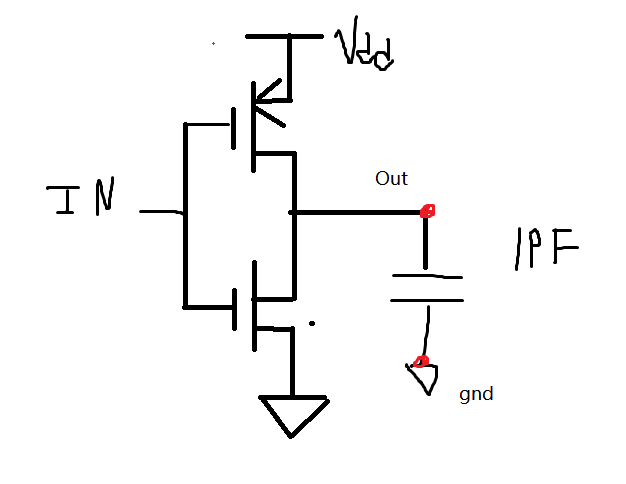

在进行PEX提参数的时候,经辛博士提醒发现一个问题,即在calibre选择transistor提参数时,电容会被提两次。以下图反相器为例。

本身在Out和gnd之间,有1pF的电容,但是在RVE界面,在CC(耦合电容)提参处也存在一个1pF的寄生。

也就是说,电容除了1pF的负载之外,它又提取了一边。

解决方法:

一、在提出的Calibre版图时,把负载电容删掉,这样就只剩C+CC的提参了,因为里面包含电容,因此剩下的就是本身电容和寄生。(这个方法极考验眼神)

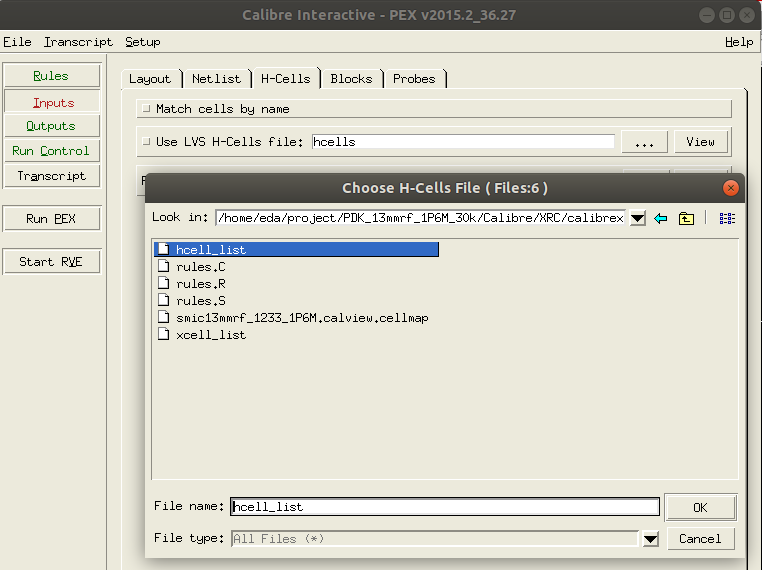

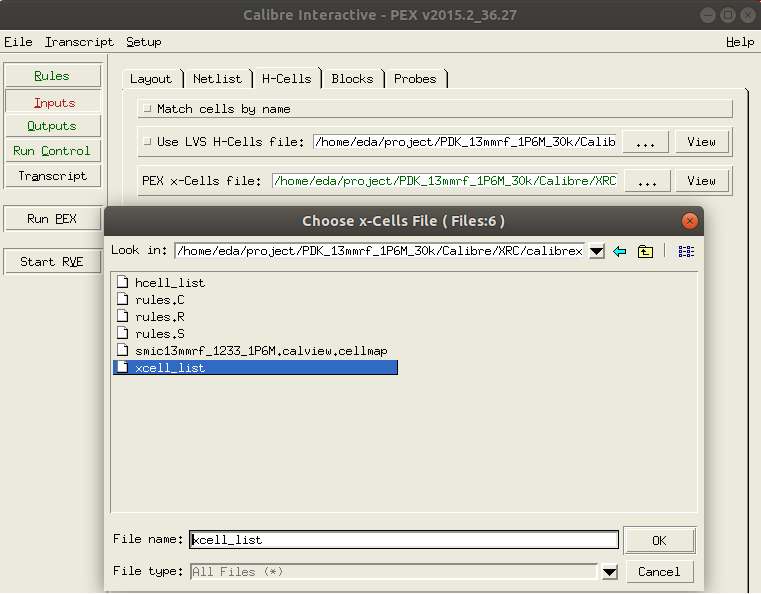

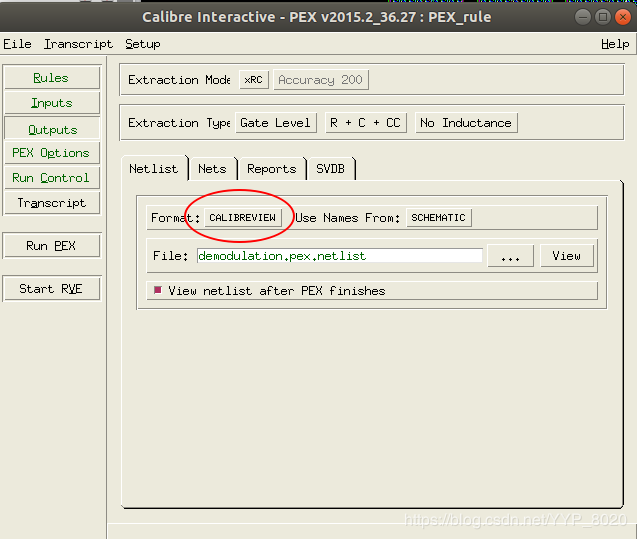

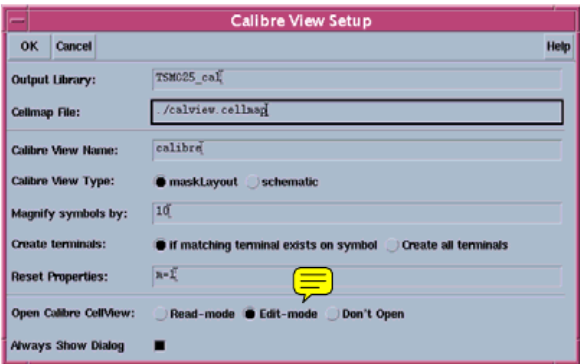

二、也是应该采用的办法,即提参时用Gate模式。不过需要在Inputs H-Cells选择hcell_list文件和xcell_list。这个xcell文件是为了避免寄生参量的重复提取。Calibre xRC提供一种称为“黑盒”的提取方法,可以将指定的器件看作理想器件,对其内部的节点之间的寄生电容和寄生电阻不再提取。选择Gate level提取。(下图网上找的)

如果LVS正确,就生成下图(下图网上找的)

Cellmap是描述寄生参量提取前后器件对应关系的文件,默认的是./calview.cellmap。

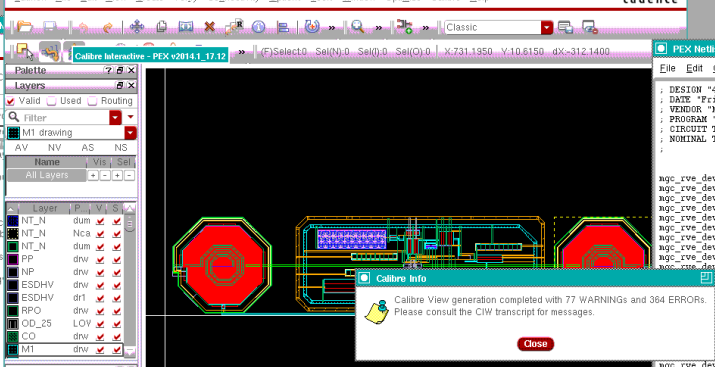

这里再确认的时候,有时候会出现错误,这是因为选择原理图模式提取时,器件距离太近导致,因此,可以选择array阵列形式,但是这种形式就是有点不利于找器件(我们通过寻找仿真的器件的直流工作点,可以观察和评估后仿真结果,用array真的有点累)。

2.后仿版图影响问题

1.输入端口匹配

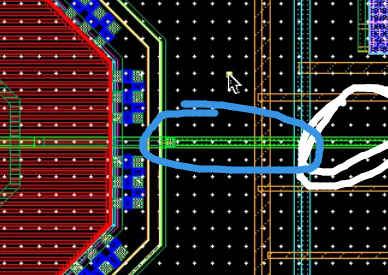

在设计输入时,由于自己做的电路输入端口有50欧的负载,开始布局时,50欧过远,且输入端口到晶体管距离过远(200um),过大的电阻导致S21变化过大(虽然S11也有影响)

左边是前仿真,右边是后仿真的S11,很明显,变化较大

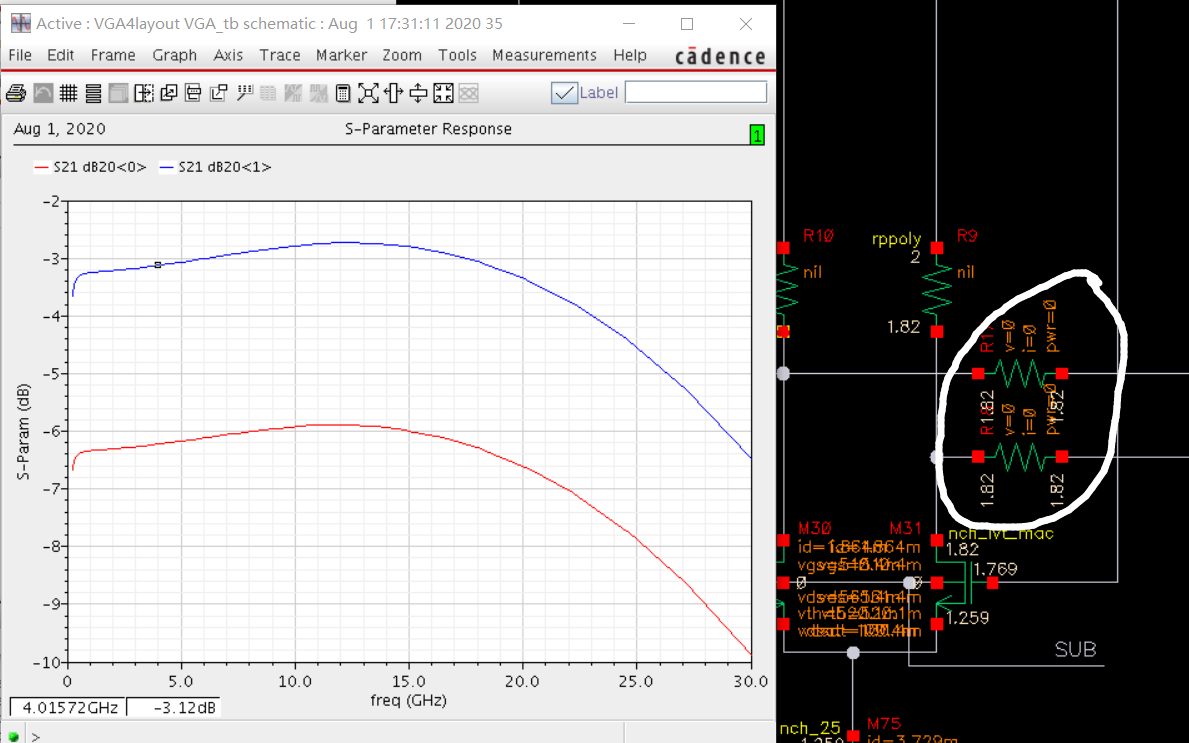

这是上面的那根长线若有寄生电阻,S21的变化曲线。很明显,带宽限制很大。

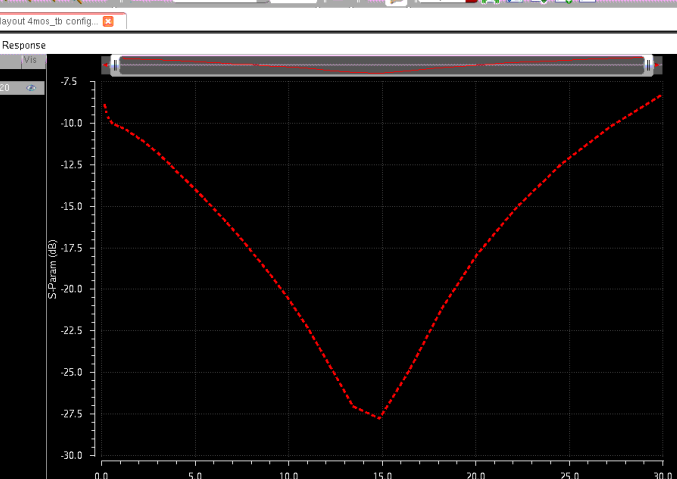

2.输出CML buffer的影响

如果输出的CML到buffer,有较长的线,那么这个寄生电阻是会很大程度降低增益的,如下图,当有几十欧姆时,会有明显的增益降低,需要注意。

3.后仿debug

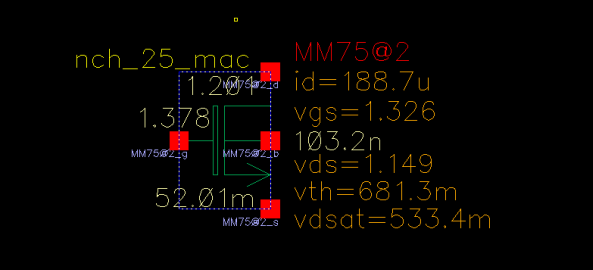

后仿时,可以通过calibre的dc工作点,来评估哪里的影响大的。后仿提参时,电路中的器件会被重新命名,如MM_器件原理图名称、器件原理图名称@2@3(这个是分段电阻和倍数个晶体管常见的表达形式),所以是可以找到的。而且,是能从结果中,看到工作点的,如下图:

图中可以看出,原本gnd是要0V的,但是,这里出现了52mV,根本原因是gnd电流流经寄生电阻引起的,因此就要降低gnd的电阻。